AMD 使用 3D 堆栈技术将 Zen 3 CPU 缓存增加三倍

首席执行官展示了一个工作 3D 堆叠的 5900X 原型

最近更新时间 2021-06-02 11:10:28

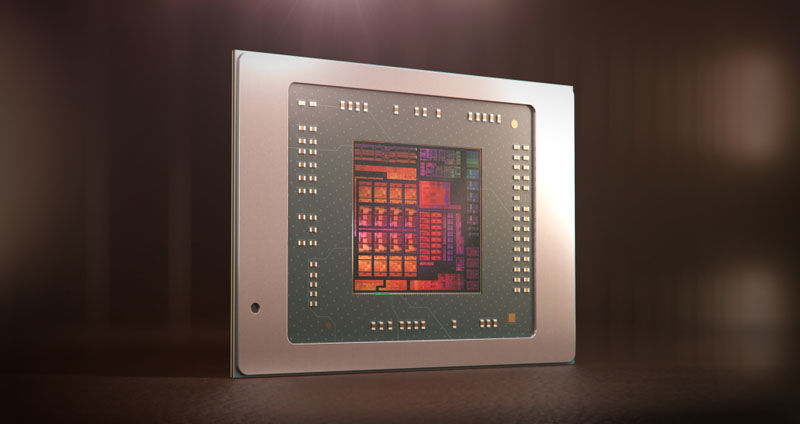

昨天在 Computex 2021 上,AMD 首席执行官 Lisa Su 展示了公司的下一个重大性能表现——3D 堆叠小芯片,使公司能够将其旗舰 Zen 3 CPU 的 L3 缓存数量增加三倍。

该技术就像它听起来的那样——一层 SRAM 缓存位于 CPU 本身的复杂核心芯片 (CCD) 之上。当前的 Zen 3 架构为每个八核小芯片集成了 32MiB 的 L3 缓存——对于像 Ryzen 9 5900X 或 5950X 这样的 12 或 16 核小芯片,总共需要 64MiB。新技术在每个小芯片的 CCD 顶部增加了一个额外的 64MiB L3 缓存,并与硅通孔 (TSV) 结合。

额外的 64MiB L3 缓存层不会扩展 CCD 的宽度,导致需要结构硅来平衡来自 CPU 冷却系统的压力。新设计中的计算和缓存芯片都变薄了,使其能够与当前的 Ryzen 5000 处理器共享基板和散热器技术。

锐龙 5000 上的 L3 缓存增加三倍,可在某些工作负载下实现性能提升 ,特别是存档压缩/解压缩和游戏,类似于在整个新一代 CPU 上看到的那些。AMD 通过战争机器 5 演示展示了性能提升。搭配未指定的 GPU 且时钟速度固定为 4 GHz,当前型号的 5900X 系统达到了 184 fps,而三重缓存原型管理 206 fps,大约提高了 12%。

AMD 声称采用新技术平均提高了 15% 的游戏性能,从英雄联盟的 4% 到怪物猎人:世界的 25% 不等。这种性能改进既不需要更小的工艺节点,也不需要更高的时钟速度,这是特别有趣的,在一个时钟速度已经基本上碰壁的时代,物理决定的进程节点收缩结束似乎也即将到来。

AMD 表示,重新设计的 5900X 将在今年晚些时候投入生产——远在 Zen 4 计划于 2022 年推出之前。 目前,AMD 只专注于“高端 Ryzen”CPU 的新技术,没有提到 Epyc。考虑到当前材料短缺,增加的缓存所需的额外芯片使其成为预算处理器的不推荐之选。